# **APPLICATION NOTE**

# RL78/F13, F14

R01AN3261EJ0100 Rev.1.00 DTC Usage Example (High-Speed Transfer and Chain Transfer) Dec 12, 2017

### Summary

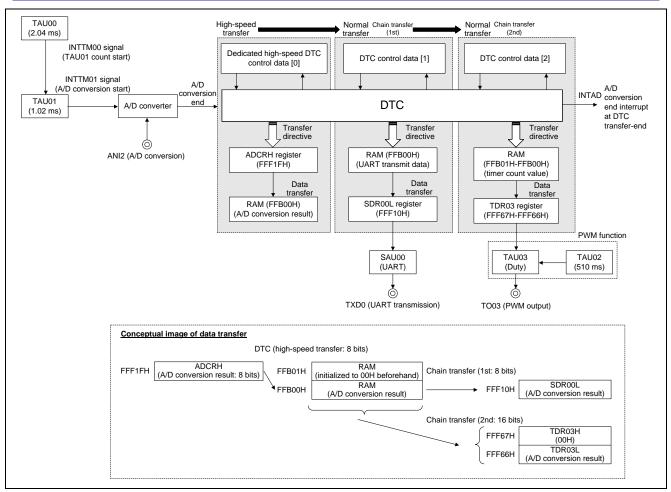

This document describes the use of the DTC (high-speed transfer and chain transfer). It explains how to use the end of A/D conversion as the DTC trigger to transfer (high-speed transfer) the A/D conversion result to RAM, to perform a serial transmission (chain transfer) of the A/D conversion result to UARTO, and to reflect (chain transfer) the A/D conversion result in the PWM output width.

## Contents

| 1.  | Overview of DTC (High-Speed Transfer and Chain Transfer) Operation             | 2    |

|-----|--------------------------------------------------------------------------------|------|

| 2.  | Specifications                                                                 | 6    |

| 3.  | Setting Procedures of Peripheral Functions                                     | .12  |

| 3.′ | 1 Peripheral Function Initialization Procedure                                 | . 12 |

| 3.2 | 2 DTC (High-Speed Transfer) and DTC (Normal Transfer) Initialization Procedure | . 13 |

| 3.: | 3 A/D Converter Initialization Procedure                                       | . 16 |

| 3.4 | 4 TAU Initialization Procedure                                                 | . 17 |

| 3.  | 5 SAU Initialization Procedure                                                 | . 19 |

| 3.0 | · · · · · · · · · · · · · · · · · · ·                                          |      |

|     | (DTC (High-Speed Transfer) Transfer Start)                                     | . 20 |

| 3.7 | 7 DTC Transfer-End Interrupt Handler                                           | . 20 |

| 4.  | Important Points                                                               | .21  |

| 4.′ | 1 DTC Transfer Cycle Count                                                     | . 21 |

| 4.2 | 2 DTC Usage Notes                                                              | . 23 |

### 1. Overview of DTC (High-Speed Transfer and Chain Transfer) Operation

The DTC of the RL78/F13 and RL78/F14 provides functionality for transferring data between areas of memory without using the CPU. There are two transfer methods: normal transfer, in which the control data is located in RAM, and high-speed transfer, which uses dedicated control data registers to allow for fewer transfer cycles than normal transfer. There are also two transfer modes (normal mode and repeat mode), and a chain transfer function that automatically continues after a transfer finishes with the next specified transfer.

During the DTC (high-speed transfer and chain transfer) operation, the DTC (high-speed transfer) initially takes place when a DTC activation source is generated. When chain transfer is enabled, the next DTC (normal transfer) then takes place and chain transfers continue until a DTC transfer with chain transfer disabled completes. All chain transfers use the normal DTC transfer method. A DTC transfer-end interrupt request is output when the first DTC (high-speed transfer) is executed, but the interrupt is held pending during DTC chain transfers. Thus, the DTC transfer-end interrupt can be accepted only when all transfers have finished.

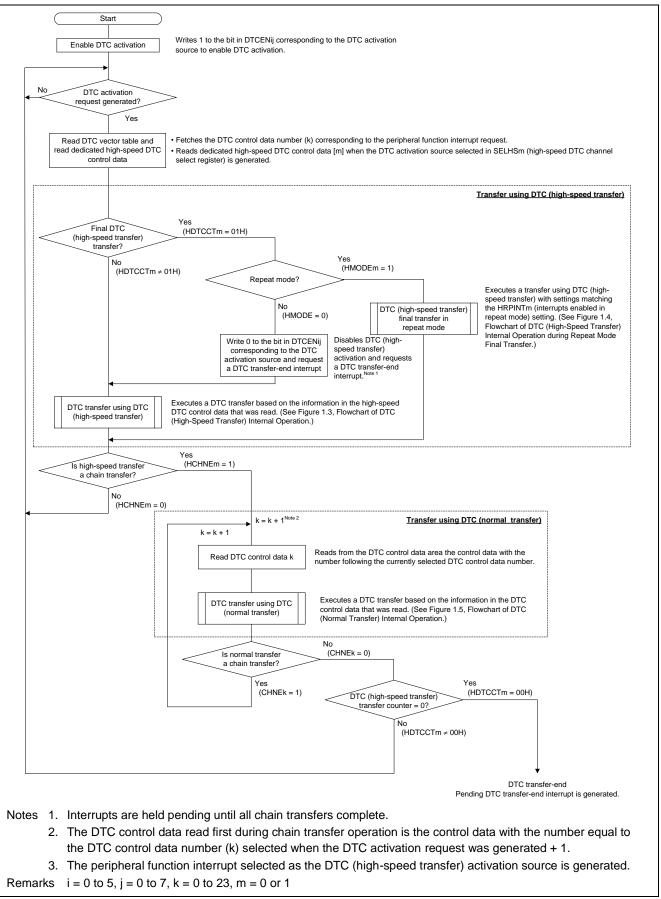

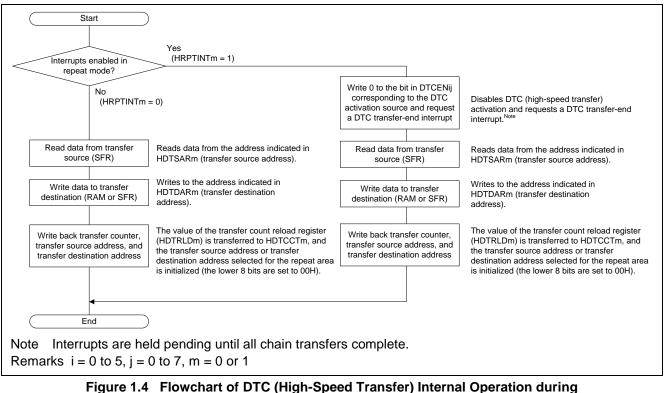

Figure 1.1 is an outline of DTC (high-speed transfer and chain transfer) operation, and Figure 1.2 to Figure 1.5 are flowcharts of DTC (high-speed transfer and chain transfer) internal operation.

|                                               |                                                                                                                                                                                                                         | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | /                                                                                                                          |                                                                             |          |                                     |                          |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|----------|-------------------------------------|--------------------------|

|                                               | Special function register                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | FFBF8H-FFBFFH                                                                                                              | DTC control data [23]                                                       |          | DTC control data [k]                |                          |

| FF00H                                         | (1st SFR)                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | FFBF0H-FFBF7H                                                                                                              | DTC control data [22]                                                       |          | DTD                                 | ARk                      |

| FEFFH                                         | General registers                                                                                                                                                                                                       | - /                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                            | :                                                                           |          | DTS                                 | ARk                      |

|                                               | General registers                                                                                                                                                                                                       | and the second se | FFB50H-FFB57H                                                                                                              | DTC control data [2]                                                        | (d)      | DTRLDk                              | DTCCTk                   |

|                                               | RAM                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | FFB48H-FFB4FH                                                                                                              | DTC control data [1]                                                        | (c)      | DTBLSk                              | DTCCRk                   |

|                                               |                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | FFB40H-FFB47H                                                                                                              | DTC control data [0]                                                        |          |                                     |                          |

|                                               |                                                                                                                                                                                                                         | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                            | Reserved area                                                               |          |                                     |                          |

|                                               | Mirror<br>Data flash memory                                                                                                                                                                                             | - \                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | FFB00H-FFB2EH                                                                                                              | DTC vector table area                                                       | (b)      | Dedicated high-speed                | d DTC control data [m]   |

|                                               | Data hash memory                                                                                                                                                                                                        | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                            |                                                                             |          | HDTD                                | ARm                      |

| 07FFH                                         |                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                            |                                                                             |          | HDTS                                | ARm                      |

|                                               | Special function register                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | F02D8H-F02DFH                                                                                                              | Dedicated high-speed DTC control data [1]                                   |          | HDTRLDm                             | HDTCCTm                  |

| 10000H                                        | (2nd SFR)                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | F02D0H-F02D7H                                                                                                              | Dedicated high-speed DTC control data [0]                                   | (a)      | —                                   | HDTCCRm                  |

|                                               | Code flash memory                                                                                                                                                                                                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                            |                                                                             |          |                                     |                          |

| 10000H                                        | Code flash memory                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                            |                                                                             |          |                                     |                          |

| correspo<br>1. E<br>2. D<br>3. C<br>d<br>4. N | eration described below occurs v<br>onding to DTC activation source<br>vent selected as DTC activation<br>redicated high-speed DTC contri-<br>tortrol data [0] indicates that the<br>ata, DTC control data [1], is rear | e, chain transfer e<br>n source of DTC<br>ol data [0] is read<br>value read from<br>d and a memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | enabled in DTC contro<br>(high-speed channel 0<br>d and a memory transi<br>the DTC vector table<br>transfer takes place (o | ,<br>er takes place (a).<br>area (b) corresponding to the activation source | e is "40 | data [2].<br>H (k = 0)." When chain | transfer starts, the nex |

Figure 1.1 Flowchart (Outline) of DTC (High-Speed Transfer and Chain Transfer) Operation

RL78/F13, F14

#### DTC Usage Example (High-Speed Transfer and Chain Transfer)

Figure 1.2 Flowchart of DTC (High-Speed Transfer and Chain Transfer) Internal Operation

Remarks m = 0 and 1

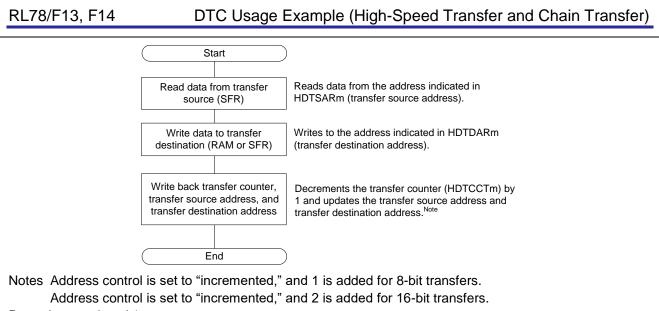

Figure 1.3 Flowchart of DTC (High-Speed Transfer) Internal Operation

Repeat Mode Final Transfer

Figure 1.5 Flowchart of DTC (Normal Transfer) Internal Operation

## 2. Specifications

A usage example combining the DTC, the A/D converter, timer array unit (TAU) channels 0 to 3 (TAU00 to TAU03), and UART0 transmission (on channel 0 (SAU00) of the serial array unit (SAU)) is presented below.

TAU00 (2.04 ms) and TAU01 (1.02 ms) count in coordinated fashion, and the A/D converter uses the TAU01 interrupt request signal as the trigger to perform A/D conversion of the input voltage on the ANI2 pin. In addition, TAU02 (510  $\mu$ s) and TAU03 count in coordinated fashion, and a PWM signal is output on the TO03 pin. Using the A/D conversion end as the DTC (high-speed transfer) activation source, the DTC starts operating and performs the following memory transfers by means of chain transfers:

- Transfer of the A/D conversion result to RAM (DTC (high-speed transfer))

- Transfer of the A/D conversion result stored in RAM to the SDR00L register (DTC (normal transfer))

- Transfer of the A/D conversion result stored in RAM to the TDR03 register (DTC (normal transfer))

After this, the above processing is repeated.

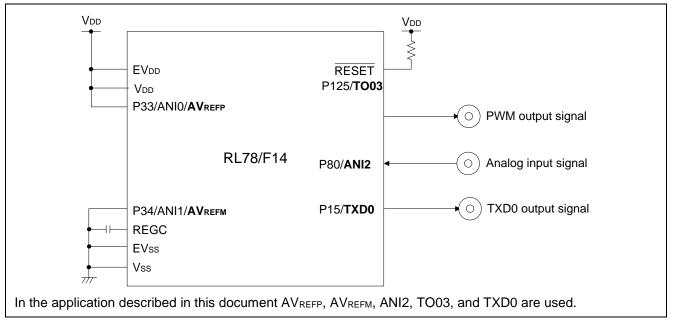

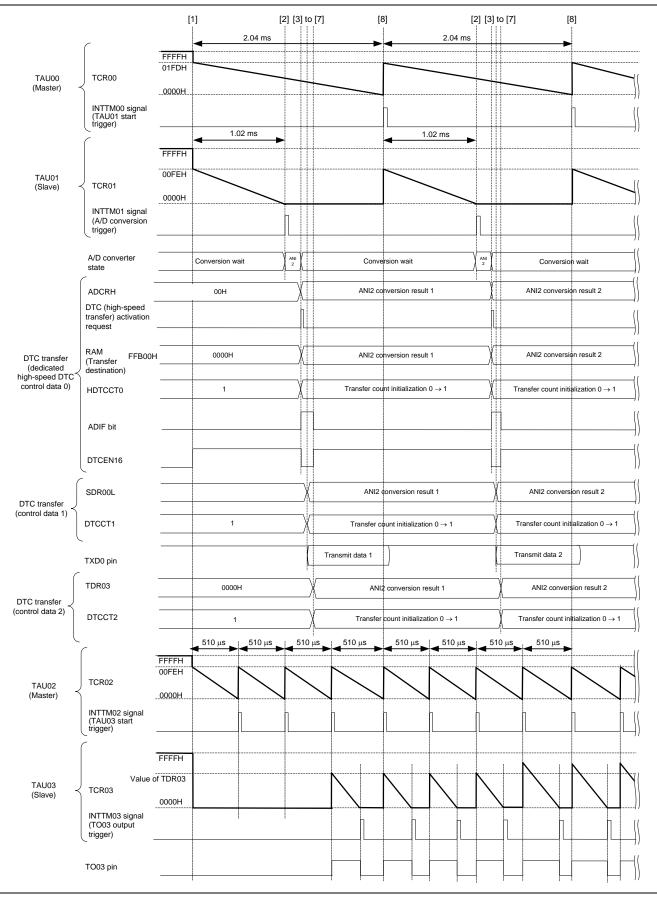

Figure 2.1 is a connection diagram showing the pins used, Table 2.1 lists the peripheral functions used and their applications, Figure 2.2 is a configuration diagram of the peripheral functions used, Figure 2.3 shows the allocation of the DTC control data and DTC vector table, and Figure 2.4 and Figure 2.5 show the DTC transfer timing.

Figure 2.1 Connection Diagram of Pins Used

| Peripheral Function            | Application                                                                                     |

|--------------------------------|-------------------------------------------------------------------------------------------------|

| A/D converter                  | Performs A/D conversion on the analog input signals from channel                                |

|                                | ANI2.                                                                                           |

|                                | 8-bit resolution                                                                                |

|                                | Hardware trigger no-wait mode (source: INTTM01)                                                 |

|                                | Select mode (1-channel)                                                                         |

|                                | One-shot conversion mode                                                                        |

| TAU00                          | Constant-period timer                                                                           |

|                                | Interval timer mode (2.04 ms)                                                                   |

|                                | Used as master channel                                                                          |

| TAU01                          | Generates A/D conversion trigger (INTTM01).                                                     |

|                                | One-count mode (1.02 ms)                                                                        |

|                                | Used as TAU00 slave channel.                                                                    |

| TAU02                          | Constant-period timer                                                                           |

|                                | Interval timer mode (510 µs)                                                                    |

|                                | Used as master channel                                                                          |

| TAU03                          | PWM signal output                                                                               |

|                                | One-count mode                                                                                  |

|                                | Output pin: TO03                                                                                |

|                                | High width: 0 to 510 μs (zero-expanded data derived from upper 8 bits of A/D conversion result) |

|                                | Used as TAU02 slave channel                                                                     |

| SAU00                          | Performs transmission on TXD0 pin in UART mode.                                                 |

|                                | Operating mode: UART mode (transmit function)                                                   |

|                                | Baud rate: 9,600 bps (error: +0.16%)                                                            |

|                                | (8 data bits, no parity, 1 stop bit, LSB-first)                                                 |

| DTC (high-speed DTC channel 0) | Transfers the A/D conversion result register value to the RAM.                                  |

|                                | DTC activation source: End of A/D conversion                                                    |

|                                | Transfer source address: ADCRH register                                                         |

|                                | Transfer destination address: RAM                                                               |

|                                | Transfer size: 1 byte                                                                           |

|                                | Transfer count: 1                                                                               |

|                                | Operating mode: Repeat mode, chain transfer enabled                                             |

| DTC (control data 1)           | Transfers the A/D conversion result register value to serial data                               |

|                                | register 00.<br>DTC activation source: —                                                        |

|                                | Transfer source address: RAM (A/D conversion result storage                                     |

|                                | destination)                                                                                    |

|                                | Transfer destination address: SDR00L register                                                   |

|                                | Transfer size: 1 byte                                                                           |

|                                | Transfer count: 1                                                                               |

|                                | Operating mode: Repeat mode, chain transfer enabled                                             |

| DTC (control data 2)           | Transfers the A/D conversion result register value to timer data register 03.                   |

|                                | DTC activation source: —                                                                        |

|                                | Transfer source address: RAM (A/D conversion result storage destination)                        |

|                                | Transfer destination address: TDR03 register                                                    |

|                                | Transfer size: 2 bytes                                                                          |

|                                | Transfer count: 1                                                                               |

|                                |                                                                                                 |

|                                | Operating mode: Repeat mode, chain transfer disabled                                            |

#### Table 2.1 Peripheral Functions Used and Their Applications

# DTC Usage Example (High-Speed Transfer and Chain Transfer)

Figure 2.2 Configuration Diagram of Peripheral Functions Used

# DTC Usage Example (High-Speed Transfer and Chain Transfer)

| F02DEH               | (SFR<br>HDTI               | ,                          |            |                                           |

|----------------------|----------------------------|----------------------------|------------|-------------------------------------------|

| F02DCH               | HDT                        |                            |            |                                           |

| F02DAH               | HDTRLD1                    | HDTCCT1                    | $\geq$     | Dedicated high-speed DTC control data [1] |

| F02D8H               |                            | HDTCCR1                    |            |                                           |

| F02D6H               | HDTI                       | DAR0                       |            |                                           |

| F02D4H               |                            | HDTSAR0                    |            |                                           |

| F02D2H               | HDTRLD0                    | HDTCCT0                    | $\leq$     | Dedicated high-speed DTC control data [0] |

| F02D0H               |                            | HDTCCR0                    |            |                                           |

| _                    | (RAM are                   | ea) <sup>Note 1</sup>      |            |                                           |

| +F8 to +FFH          | Control                    | data [23]                  |            |                                           |

| +F0 to +F7H          | Control                    | data [22]                  |            |                                           |

| :                    |                            | :                          |            |                                           |

| +58 to +5FH          | Control                    | data [3]                   | ~          |                                           |

| +56H                 | DTD                        | AR2                        |            |                                           |

| +54H                 | DTS                        | AR2                        |            | Control data [2]                          |

| +52H                 | DTRLD2                     | DTCCT2                     |            | L J                                       |

| +50H                 | DTBLS2                     | DTCCR2                     | $ \langle$ |                                           |

| +4EH                 | DTD                        |                            |            |                                           |

| +4CH                 | DTS                        |                            |            | Control data [1]                          |

| +4AH                 | DTRLD1                     | DTCCT1                     |            |                                           |

| +48H                 | DTBLS1                     | DTCCR1                     | $ \langle$ |                                           |

| +46H                 |                            | AR0                        |            |                                           |

| +44H                 |                            | AR0                        |            | Control data [0]                          |

| +42H                 | DTRLD0                     | DTCCT0                     |            |                                           |

| +40H                 | DTBLSO                     | DTCCR0                     |            |                                           |

| +2EH to +3FH<br>+2CH |                            | ed area                    |            |                                           |

| +2011                | (INTTM17)                  | (INTTM16)<br>(INTTM14)     |            |                                           |

| +28H                 | (INTTM15)<br>(INTLIN1TRM)  | (INTLIN1RVC)               |            |                                           |

| +26H                 | (INTTM13)                  | (INTTM12)                  |            |                                           |

| +24H                 | (INTTM13)<br>(INTTM11)     | (INTTM12)<br>(INTTM10)     |            |                                           |

| +22H                 | (INTCMP0)                  | (INTRJ0)                   |            |                                           |

| +20H                 | (TRDSR1.IMFD)              | (TRDSR1.IMFC)              |            |                                           |

| +1EH                 | (TRDSR1.IMFB)              | (TRDSR1.IMFA)              |            |                                           |

| +1CH                 | (TRDSR0.IMFD)              | (TRDSR0.IMFC)              |            |                                           |

| +1AH                 | (TRDSR0.IMFB)              | (TRDSR0.IMFA)              |            |                                           |

| +18H                 | (INTTM07)                  | (INTTM06)                  |            |                                           |

| +16H                 | (INTTM05)                  | (INTTM04)                  |            | DTC vector table area                     |

| +14H                 | (INTTM03)                  | (INTTM02)                  |            |                                           |

| +12H                 | (INTTM01)                  | (INTTM00)                  |            |                                           |

| +10H                 |                            | (INTCANGRFR)               |            |                                           |

| +0EH                 | (INTLINOTRM)               | (INTLINORVC)               |            |                                           |

| +0CH                 | (INTST1) <sup>Note 2</sup> | (INTSR1) <sup>Note 3</sup> |            |                                           |

| +0AH                 | (INTST0) <sup>Note 4</sup> | (INTSR0) <sup>Note 5</sup> |            |                                           |

| +08H                 | (INTAD)                    | (INTKR)                    |            |                                           |

|                      | (INTP6)                    | (INTP5)                    |            |                                           |

| +06H                 | ( <b></b>                  | (INTP3)                    |            |                                           |

| +06H<br>+04H         | (INTP4)                    | (11110)                    |            |                                           |

| +06H                 | (INTP4)<br>(INTP2)         | (INTP1)                    |            |                                           |

- 2. INTST1/INTCSI10/INTIIC10

- 3. INTSR1/INTCSI11/INTIIC11

- 4. INTSTO/INTCSI00/INTIIC00

- 5. INTSR0/INTCSI01/INTIIC01

#### Figure 2.3 Allocation of DTC Control Data and DTC Vector Table

RL78/F13, F14

# DTC Usage Example (High-Speed Transfer and Chain Transfer)

Figure 2.4 DTC Transfer Timing (1/2)

[1] The following register settings are made by the software to put the function in the operational state: • The DTCEN16 bit in the DTCEN1 register is set to 1 (DTC activation enabled (source: A/D conversion end)). • The TS00, TS01, TS02, and TS03 bits in the TS0 register are set to 1 (start counting on TAU00, TAU01, TAU02, and TAU03). • The SE00 bit in the SS0 register is set to 1 (SAU0 CH0 in transmit-standby state). [2] When TAU01 finishes counting, the INTTM01 signal is output. Also, A/D conversion starts, using this signal as the trigger. [3] After A/D conversion end, the ADIF bit changes to 1 and a DTC (high-speed transfer) memory transfer is performed (ADCRH register  $\rightarrow$  RAM), using the A/D conversion-end interrupt request signal as the trigger. Also, the HDTCCT0 register is decremented when the DTC transfer occurs. [4] When the transfer that causes the value of the HDTCCT0 register to change from 1 to 0 is executed, the following operations are performed: The DTCEN16 bit is cleared to 0 (DTC activation disabled). • An A/D conversion-end interrupt request is generated due to the DTC (high-speed transfer) transfer end. (Generation of interrupts is held pending until all DTC transfers using chain transfer complete.) • A data transfer using DTC (high-speed transfer) is executed (ADCRH register  $\rightarrow$  RAM). • The value of the HDTRLD0 register is stored in the HDTCCT0 register (initialization of transfer count using DTC (high-speed transfer)). [5] After confirmation that the HCHNE0 bit in the HDTCCR0 register has been set to 1, control data 1 is read from the control data area and the following operations are performed: A data transfer using DTC (normal transfer) is executed (RAM (A/D conversion result storage area) → SDR00L register). • The DTCCT1 register is decremented. Also, SAU0 transmits the A/D conversion result on the TXD0 pin due to the data transfer to the SDR00L register. [6] After confirmation that the CHNE bit in the DTCCR1 register has been set to 1, control data 2 is read from the control data area and the following operations are performed: • A data transfer using DTC (normal transfer) is executed (RAM (16-bit extended value from A/D conversion result storage area) → TDR03 reaister). • The DTCCT2 register is decremented. [7] An A/D conversion-end interrupt request is generated due to the DTC transfer end. At this point the following settings are made by the software: • The software sets the DTCEN16 bit in the DTCEN1 register to 1 (DTC (high-speed transfer) activation enabled). [8] TAU00 and TAU01 perform the following operations: • An INTTM00 signal is output when the TAU00 count completes (generation of TAU00 interrupt request signal). • TAU01 (slave) starts counting. Also, TAU02 and TAU03 perform the following operations during steps [2] to [8]: An INTTM02 signal is output when the TAU02 count completes (generation of TAU02 interrupt request signal), and the TO03 pin is driven to the high level (unless the value of the TDR03 register is 0000H). TAU03 (slave) starts counting. • The TO03 pin is driven to the low level when the TAU03 count completes. Notes TCR00: Timer counter register 00 INTTM00 signal: Timer channel 0 count-end/capture-end interrupt request signal TCR01: Timer counter register 01 INTTM01 signal: Timer channel 1 count-end/capture-end interrupt request signal (Used as A/D conversion trigger.) A/D conversion status: 10-bit successive approximation register ADCRH: 8-bit A/D conversion result register (upper 8 bits of ADCR) DTC (high-speed transfer) activation request: Single-channel A/D conversion-end interrupt signal FFB00H: RAM indicating HDTDAR0 (high-speed DTC transfer destination address register) for A/D conversion result storage HDTCCT0: High-speed DTC transfer count register 0 ADIF bit: A/D conversion end interrupt flag DTCEN16: DTCEN16 bit in DTCEN1 register SDR00L: Serial data register 00 (lower 8 bits of SDR00) TXD0 pin: UART0 transmit pin DTCCT1: DTC transfer count register 1 allocated in DTC control data area TCR02: Timer counter register 02 INTTM02 signal: Timer channel 2 count-end/capture-end interrupt request signal TCR03: Timer counter register 03 INTTM03 signal: Timer channel 3 count-end/capture-end interrupt request signal TDR03: Timer data register 3 TO03 pin: Timer channel 3 PWM signal output pin DTCCT2: DTC transfer count register 2 allocated in DTC control data area CK03 (f<sub>CLK</sub> / 128 = 250 kHz) selected as TAU00 and TAU01 count clock CK02 (f<sub>CLK</sub> / 64 = 500 kHz) selected as TAU02 and TAU03 count clock

#### Figure 2.5 DTC Transfer Timing (2/2)

# 3. Setting Procedures of Peripheral Functions

The setting procedures of the peripheral functions (DTC, A/D converter, TAU, and SAU), are described in this section.

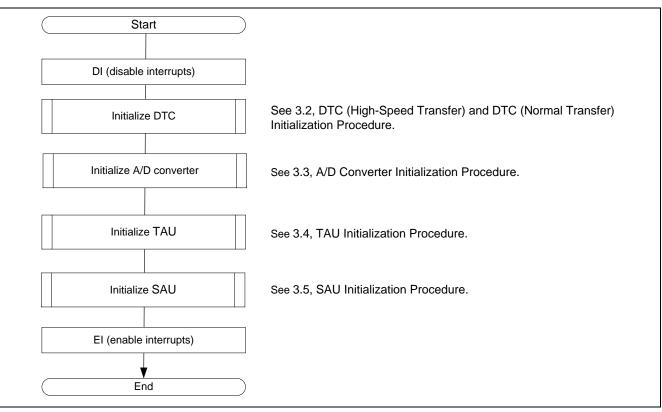

# 3.1 Peripheral Function Initialization Procedure

Figure 3.1 shows the peripheral function initialization procedure.

Figure 3.1 Peripheral Function Initialization Procedure

#### 3.2 DTC (High-Speed Transfer) and DTC (Normal Transfer) Initialization Procedure

Using the end of A/D conversion as the activation source, the A/D conversion result is transferred (high-speed transfer) to the conversion result storage area in RAM, the A/D conversion result stored in the A/D conversion result storage area is transferred (chain transfer) to the SDR00L register, and the A/D conversion result stored in the A/D conversion result storage area (16-bit expanded) is transferred (chain transfer) to the TDR03 register, sequentially.

Figure 3.2 and Figure 3.3 show the DTC (high-speed transfer) and DTC (normal transfer) initialization procedure. Figure 3.4 shows the allocation of DTC control data.

| Start                                                                          | )                                                                                                                                                                                                                         |

|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                |                                                                                                                                                                                                                           |

| FFD00H to FFDFFH = 00H                                                         | Initializes the DTC control data area and DTC vector table area (00H).                                                                                                                                                    |

|                                                                                | 1                                                                                                                                                                                                                         |

| PER1.DTCEN = 1                                                                 | Supplies the DTC input clock.                                                                                                                                                                                             |

| DTCENi = 00H<br>(i = 0 to 5)                                                   | Disables all DTC activation.                                                                                                                                                                                              |

| DTCBAR = FDH                                                                   | Sets the DTC base address. (FFD00H)<br>(DTC vector address : FFD00H<br>DTC control data area start address : FFD40H                                                                                                       |

| FFD09H address = 40H                                                           | Selects DTC control data 0 as DTC vector table source number [9] (A/D conversion end). (Stores the lowest 1 byte of the DTC control data 0 address (FFD40H).)                                                             |

| SELHS0 = 09H                                                                   | Selects activation source number 9 (A/D conversion end) for high-speed DTC channel 0.                                                                                                                                     |

| HDTCCR0 = 31H                                                                  | Sets the dedicated high-speed control data [0] conditions:<br>8 data bits, repeat mode, interrupts enabled in repeat mode, chain transfer<br>enabled, transfer source address fixed, transfer destination is repeat area. |

| HDTCCT0 = 01H                                                                  | Sets the transfer count (1 time).                                                                                                                                                                                         |

| HDTRLD0 = 01H                                                                  | Sets the transfer count (reload) (1 time).                                                                                                                                                                                |

| HDTSAR0 = 0F1FH                                                                | Sets the transfer source address (lower 12 bits of address data in ADCRH register)                                                                                                                                        |

| HDTDAR0 = FB00H                                                                | Sets the transfer destination address (lower 2 bytes of address data in RAM)                                                                                                                                              |

|                                                                                |                                                                                                                                                                                                                           |

| To Figure 3.3, DTC (High-Speed Tran<br>Transfer) Initialization Procedure (2/2 |                                                                                                                                                                                                                           |

Figure 3.2 DTC (High-Speed Transfer) and DTC (Normal Transfer) Initialization Procedure (1/2)

| From Figure 3.2, DTC (High-Speed To<br>Initialization Procedure (1/2) | ransfer) and DTC (Normal Transfer)                                                                                                                                                                    |

|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                       |                                                                                                                                                                                                       |

| DTCCR1 = 13H                                                          | Sets the control data 1 conditions:<br>8 data bits, repeat mode, interrupts disabled in repeat mode, chain transfer<br>enabled, transfer destination address fixed, transfer source is repeat area.   |

| DTBLS1 = 01H                                                          | Sets the transfer size (1 byte).                                                                                                                                                                      |

| DTCCT1 = 01H                                                          | Sets the transfer count (1 time).                                                                                                                                                                     |

| DTRLD1 = 01H                                                          | Sets the DTC transfer count (reload) (1 time).                                                                                                                                                        |

| DTSAR1 = FB00H                                                        | Sets the transfer source address (lower 2 bytes of address data in RAM)                                                                                                                               |

| DTDAR1 = FF10H                                                        | Sets the transfer destination address (lower 2 bytes of address data in SDR00L)                                                                                                                       |

| DTCCR2 = 43H                                                          | Sets the control data 2 conditions:<br>16 data bits, repeat mode, interrupts disabled in repeat mode, chain transfer<br>disabled, transfer destination address fixed, transfer source is repeat area. |

| DTBLS2 = 01H                                                          | Sets the transfer size (1 byte).                                                                                                                                                                      |

| DTCCT2 = 01H                                                          | Sets the transfer count (1 time).                                                                                                                                                                     |

| DTRLD2 = 01H                                                          | Sets the transfer count (reload) (1 time).                                                                                                                                                            |

| DTSAR2 = FB00H                                                        | Sets the transfer source address (lower 2 bytes of address data in RAM)                                                                                                                               |

| DTDAR2 = FF66H                                                        | Sets the transfer destination address (lower 2 bytes of address data in TDR03)                                                                                                                        |

|                                                                       |                                                                                                                                                                                                       |

| ( End )                                                               |                                                                                                                                                                                                       |

Figure 3.3 DTC (High-Speed Transfer) and DTC (Normal Transfer) Initialization Procedure (2/2)

|                 | (SFR area)                        | 1.                                                                                |

|-----------------|-----------------------------------|-----------------------------------------------------------------------------------|

| F02DEH          | HDTDAR1                           |                                                                                   |

| F02DCH          | HDTSAR1                           | <ul> <li>Dedicated high-speed DTC control data [1]</li> </ul>                     |

| F02DAH          | HDTRLD1 HDTCCT1                   |                                                                                   |

| F02D8H          | — HDTCCR1                         |                                                                                   |

| F02D6H          | HDTDAR0 = FB00H                   | Dedicated high-speed DTC control data [0]                                         |

| F02D4H          | HDTSAR0 = 0F1FH                   | Activation source: A/D conversion end                                             |

| F02D2H          | HDTRLD0 = 01H HDTCCT0 = 01H       | 8-bit transfer from transfer source (ADCRH) to transfer destination RAM (FFB00H)  |

| F02D0H          | — HDTCCR0 = 31H                   | Transfer count: 1 time, repeat mode, chain transfer enabled, interrupts enabled   |

|                 |                                   |                                                                                   |

|                 |                                   |                                                                                   |

|                 | (RAM area) <sup>Note</sup>        |                                                                                   |

|                 | Control data [23]                 |                                                                                   |

|                 | Control data [22]                 |                                                                                   |

|                 | :                                 |                                                                                   |

|                 | Control data [3]                  |                                                                                   |

| FFD56H          | DTDAR2 = FF66H                    | Control data [2]                                                                  |

| FFD54H          | DTSAR2 = FB00H                    | Activation source: DTC (normal transfer, control data [1]) transfer end           |

| FFD52H          | DTRLD2 = 01H DTCCT2 = 01H         | 16-bit transfer from transfer source RAM (FFB00H) to transfer destination (TDR03) |

| FFD50H          | DTBLS2 = 01H DTCCR2 = 43H         | Transfer count: 1 time, repeat mode, chain transfer disabled, interrupts disabled |

| FFD4EH          | DTDAR1 = FF10H                    | Control data [1]                                                                  |

| FFD4CH          | DTSAR1 = FB00H                    | Activation source: DTC (high-speed transfer) transfer end                         |

| FFD4AH          | DTRLD1 = 01H DTCCT1 = 01H         | 8-bit transfer from transfer source RAM (FFB00H) to transfer destination (SDR00L) |

| FFD48H          | DTBLS1 = 01H DTCCR1 = 13H         | Transfer count: 1 time, repeat mode, chain transfer enabled, interrupts disabled  |

| FFD46H          | DTDAR0                            |                                                                                   |

| FFD44H          | DTSAR0                            |                                                                                   |

| FFD42H          | DTRLD0 DTCCT0                     | Control data [0]                                                                  |

| FFD40H          | DTBLS0 DTCCR0                     |                                                                                   |

| FFD2E to FFD3FH | Reserved area                     |                                                                                   |

| FFD09 to FFD2DH | :                                 |                                                                                   |

| FFD08H          | (INTAD) = 40H (INTKR)             | $\succ$ vector table area                                                         |

| FFD00 to FFD07H | :                                 |                                                                                   |

| Note When F     | DH is set in the DTCBAR regis     | ster (DTC control data and DTC vector table start address set to                  |

| FFD00H          |                                   |                                                                                   |

|                 | ,                                 | ocument, the DTC activation source (INTAD) causes the register                    |

|                 |                                   |                                                                                   |

|                 |                                   | h-speed DTC control data [0] to be read and DTC (high-speed                       |

| trans           | sfer) to take place based on tha  | at register information.                                                          |

| The             | register information read from    | dedicated high-speed DTC control data [0] indicates that chain                    |

|                 |                                   | information stored in the next control data (in this case, control                |

|                 |                                   |                                                                                   |

|                 |                                   | t register information DTC (normal transfer) takes place.                         |

| The             | register information read from    | control data [1] also indicates that chain transfer is enabled, so                |

| the r           | register information stored in th | e next control data (in this case, control data [2]) is read, and                 |

|                 | 0                                 | DTC (normal transfer) takes place.                                                |

|                 | -                                 |                                                                                   |

|                 | •                                 | control data [2] indicates that chain transfer is disabled, so DTC                |

| chai            | n transfer ends.                  |                                                                                   |

|                 |                                   |                                                                                   |

## Figure 3.4 Allocation of DTC Control Data

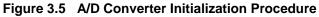

# 3.3 A/D Converter Initialization Procedure

The following settings are used to perform A/D conversion of the analog input signals on channel ANI2.

Figure 3.5 shows the initialization procedure for the A/D converter.

| Start                                |                                                                                                                                                                         |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                      |                                                                                                                                                                         |

| PER0.ADCEN = 1                       | Supplies the input clock to the A/D converter.                                                                                                                          |

| ADPC = 04H                           | Analog input port settings<br>Selects analog input for P33/ANI0/AV <sub>REFP</sub> , P34/ANI1/AV <sub>REFM</sub> , and P80/ANI2.                                        |

|                                      |                                                                                                                                                                         |

| PM3.PM3[4:3] = 11B<br>PM8.0 = 1      | Sets used analog input pins to input mode                                                                                                                               |

|                                      | A/D converter operating mode settings (ADM0 register)ADCS: 0B (A/D converter operation stop selected)ADMD: 0B (scan mode selected as conversion channel selection mode) |

| ADM0 = 2AH                           | FR[2:0]       : 101B (f <sub>CLK</sub> /5 selected as conversion clock)         LV[1:0]       : 01B (normal 2 selected as conversion mode)                              |

|                                      | ADCE : 0B (A/D comparator operation stop selected)                                                                                                                      |

|                                      | A/D converter operating mode settings (ADM1 register)                                                                                                                   |

| ADM1 = A0H                           | ADTMD[1:0] : 10B (hardware trigger no-wait mode selected)<br>ADCSM : 1B (one-shot conversion mode selected)                                                             |

|                                      | ADTRS[1:0] : 00B (TAU01 selected as hardware trigger)                                                                                                                   |

|                                      | A/D converter operating mode settings (ADM2 register)                                                                                                                   |

|                                      | ADREFP[1:0] : 01B (AV <sub>REFP</sub> selected as + side reference voltage source)                                                                                      |

|                                      | ADREFM : 1B (AV <sub>REFM</sub> selected as – side reference voltage source)<br>ADRCK : 0B (generation of interrupt signal (INTAD) when ADLL register                   |

| ADM2= 61H                            | ADCR register < ADUL register when checking conversion<br>results selected)                                                                                             |

|                                      | AWC: 0B (SNOOZE mode function not used)ADTYP: 1B (8-bit selected as A/D conversion resolution)                                                                          |

| ADUL= FFH                            | Sets the upper and lower limit values for the conversion results.                                                                                                       |

| ADLL = 00H                           | Sets the upper and lower limit values for the conversion results.                                                                                                       |

| ADS = 02H                            | Analog input channel settings<br>ADISS: 0B, ADS[4:0]: 0010B (ANI2)                                                                                                      |

| A/D stabilization wait time A (5 μs) | Wait for stabilization (5 $\mu$ s) when changing ADM2.ADREFP[1:0] to 10B (+ side reference voltage source supplied from internal reference voltage (1.45 V)).           |

| ADM0.ADCE = 1                        | Enables A/D voltage comparator operation.                                                                                                                               |

| A/D stabilization wait time B (1 µs) | After setting the ADCE bit to 1, it is necessary to wait for stabilization (1 $\mu$ s) before setting the ADM0.ADCS bit to 1 (A/D converter operation enabled).         |

| PR11H.ADPR1 = 0                      | A/D conversion end interrupt priority setting                                                                                                                           |

| PR01H.ADPR0 = 1                      | 01B (level 1)                                                                                                                                                           |

| MK1H.ADMK = 0                        | Enables the A/D conversion end interrupt handler.                                                                                                                       |

| IF1H.ADIF = 0                        | Clears the A/D conversion end interrupt request signal.                                                                                                                 |

|                                      |                                                                                                                                                                         |

| End                                  |                                                                                                                                                                         |

|                                      |                                                                                                                                                                         |

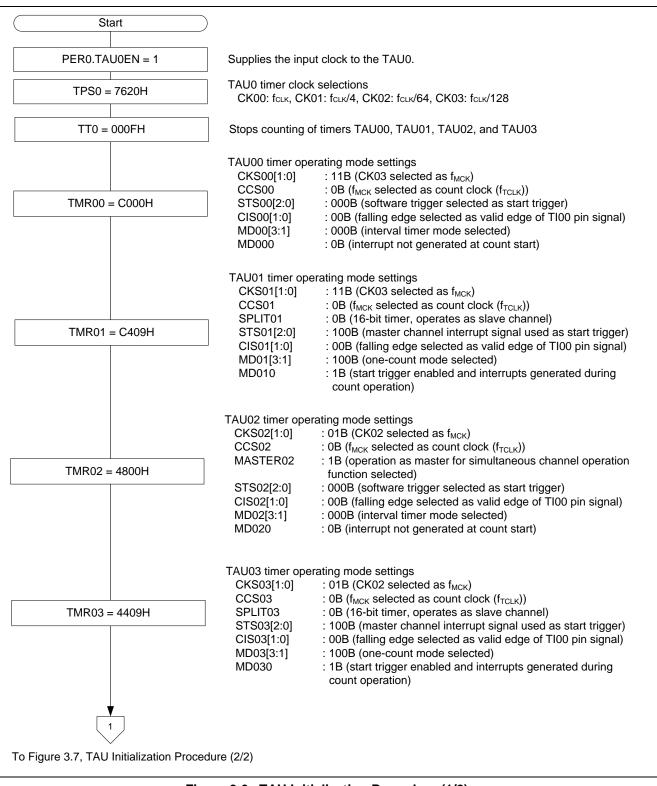

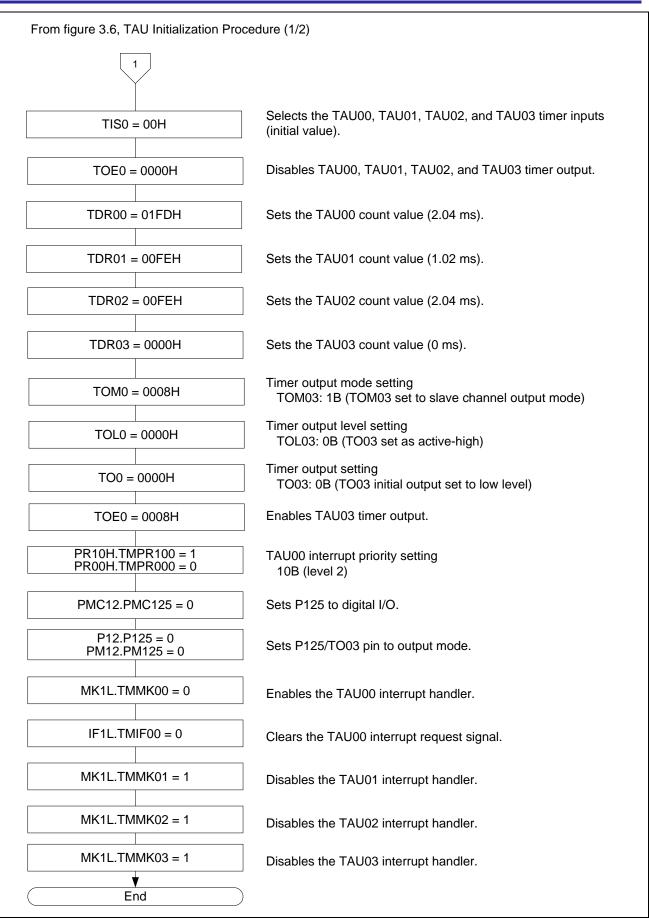

#### 3.4 TAU Initialization Procedure

TAU00 is set as a timer with a period of 2.04 ms and TAU01 is set to 1.02 ms as the slave channel of TAU00. Next, TAU02 is set as the master channel and TAU03 as the slave channel with a period of 510  $\mu$ s for use as a PWM function.

Figure 3.6 and Figure 3.7 show the TAU initialization procedure.

Figure 3.6 TAU Initialization Procedure (1/2)

Figure 3.7 TAU Initialization Procedure (2/2)

## 3.5 SAU Initialization Procedure

Settings are made to enable SAU0 to transmit in UART mode.

Figure 3.8 shows the SAU initialization procedure.

| Start                                |                                                                                                                                                        |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                      | Cumplice the imputed at the CALLO                                                                                                                      |

| PER0.SAU0EN = 1                      | Supplies the input clock to the SAU0.                                                                                                                  |

| SPS0 = 0044H                         | SAU0 cereal clock selections<br>CK00: fcLk/16, CK01 : fcLk/16                                                                                          |

| ST0 = 0003H                          | Stops SAU0 (UART0) operation.                                                                                                                          |

| SMR00 = 0022H                        | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                   |

|                                      | MD00[2:1]: 01B (UART mode selected)MD000: 0B (transfer-end interrupt selected)                                                                         |

|                                      | UART0 (SAU00) communication operation settings<br>TXE00, RXE00 : 10B (transmission selected as operating mode)<br>DAP00, CKP00 : 00B (type 1 selected) |

| SCR00 = 8097H                        | PTC00[1:0]: 00B (no parity bit output selected)DIR00: 1B (LSB-first selected as data transfer order)                                                   |

|                                      | SLC00[1:0]: 01B (1 bit selected as number of stop bits)DLS00[3:0]: 0111B (8 bits selected as number of data bits)                                      |

| SDR00 = CE00H                        | Operating clock division ratio selection<br>SDR00[15:9] : 1100111B (f <sub>MCK</sub> /208 selected as transfer clock)                                  |

| SOL0 = 0000H                         | Selects unmodified output of transmit data (initial setting).                                                                                          |

| SO0 = 0303H                          | SO00: 1B (high level selected as initial output level of TXD0 pin)<br>Others are set to default values.                                                |

| SOE0 = 0001H                         | Enables output using SAU0 (UART0) serial communication.                                                                                                |

| P1.P15 = 1<br>PM1.PM15 = 0           | Sets P15/TXD0 pin to output mode.                                                                                                                      |

| PR10H.STPR10 = 1<br>PR00H.STPR00 = 1 | UART0 (transmit) transfer-end interrupt priority setting 11B (level 3 (low priority))                                                                  |

| MK0H.STMK0 = 1                       | Disables UART0 (transmit) interrupt processing.                                                                                                        |

| ( End )                              |                                                                                                                                                        |

|                                      | 3.8 SALL Initialization Procedure                                                                                                                      |

Figure 3.8 SAU Initialization Procedure

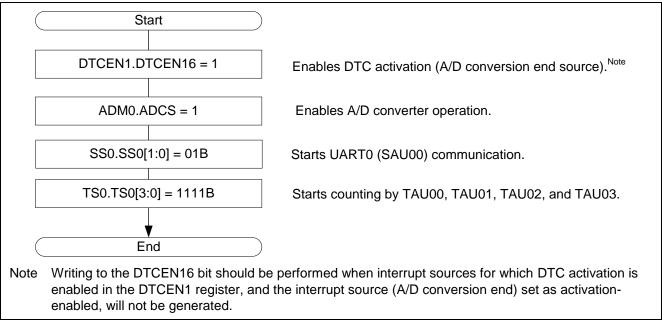

### 3.6 Procedure for Enabling Peripheral Functions (DTC (High-Speed Transfer) Transfer Start)

After initializing the peripheral functions (DTC, A/D converter, TAU, and SAU), the operation of the peripheral functions is enabled (started).

Figure 3.9 shows the procedure for enabling the operation of the peripheral functions (DTC (high-speed transfer) transfer start).

Figure 3.9 Procedure for Enabling Peripheral Functions (DTC (High-Speed Transfer) Transfer Start)

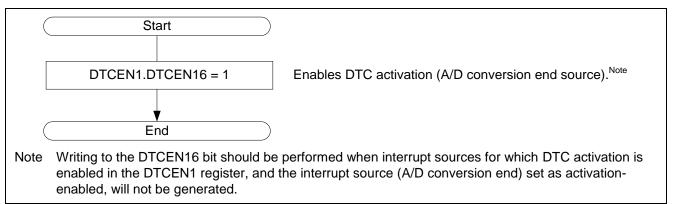

# 3.7 DTC Transfer-End Interrupt Handler

When DTC transfer ends, the corresponding interrupt (in the example presented in this document, the A/D conversionend interrupt) is generated. Figure 3.10 shows the handling of the DTC transfer-end interrupt (A/D conversion-end interrupt) in which the DTC transfer operation is re-enabled.

Figure 3.10 DTC Transfer-End Interrupt (A/D Conversion End Interrupt) Handler

#### 4. Important Points

#### 4.1 DTC Transfer Cycle Count

The minimum number of transfer clock cycles is 8 for DTC (normal transfer) and 4 for DTC (high-speed transfer). Using the DTC specifications in the usage example presented in this document, each transfer (consisting of one high-speed transfer + two normal transfers executed as chain transfers) requires 20 clock cycles. For details, refer to Table 4.1.

| Transfer               | Transfer | Transfer    | Vector | Control Data |                | Data | Data  |       |

|------------------------|----------|-------------|--------|--------------|----------------|------|-------|-------|

| Туре                   | Source   | Destination | Read   | Read         | Write-<br>Back | Read | Write | Total |

| High-speed<br>transfer | ADCRH    | RAM         |        | 1            | 1              | 1    | 1     | 4     |

| Normal<br>transfer     | RAM      | SDR00L      |        | 4            | 2              | 1    | 1     | 8     |

| Normal<br>transfer     | RAM      | TDR03       |        | 4            | 2              | 1    | 1     | 8     |

Note See Table 4.2 and Table 4.3 for the control data write-back clock cycle count, Table 4.4 and Table 4.5 for the data read clock cycle count, and Table 4.6 and Table 4.7 for the data write clock cycle count. The settings used in the example presented in this document are indicated in Table 4.2 to Table 4.7 by the white unshaded cells.

| Table 4.2 | Clock C | ycle Count N | lecessary for | DTC C | Control D | ata Write-Back |

|-----------|---------|--------------|---------------|-------|-----------|----------------|

|-----------|---------|--------------|---------------|-------|-----------|----------------|

|       | DTCCR register |        |      | Address Fixe       | d/Incremented           | Write-Back Control Data Area Registers |            |            | isters     | Clock  |

|-------|----------------|--------|------|--------------------|-------------------------|----------------------------------------|------------|------------|------------|--------|

| DAMOD | SAMOD          | RPTSEL | MODE | Transfer<br>Source | Transfer<br>Destination | DTCCTj                                 | DTRLDj     | DTSARj     | DTDARj     | Cycles |

| 0     | 0              | Х      | 0    | Fixed              | Fixed                   | Write-back                             | Write-back | —          | —          | 1      |

| 0     | 1              | Х      | 0    | Incremented        | Fixed                   | Write-back                             | Write-back | Write-back | —          | 2      |

| 1     | 0              | Х      | 0    | Fixed              | Incremented             | Write-back                             | Write-back | —          | Write-back | 2      |

| 1     | 1              | Х      | 0    | Incremented        | Incremented             | Write-back                             | Write-back | Write-back | Write-back | 3      |

| 0     | Х              | 1      | 1    | Repeat             | Fixed                   | Write-back                             | Write-back | Write-back | —          | 2      |

| 1     | Х              | 1      | 1    | Repeat             | Incremented             | Write-back                             | Write-back | Write-back | Write-back | 3      |

| Х     | 0              | 0      | 1    | Fixed              | Repeat                  | Write-back                             | Write-back | —          | Write-back | 2      |

| х     | 1              | 0      | 1    | Incremented        | Repeat                  | Write-back                             | Write-back | Write-back | Write-back | 3      |